# Methods for Evaluating and Covering the Design Space during Early Design Development

Matthias Gries

CAD-Group, Electronics Research Laboratory

University of California at Berkeley

email: gries@eecs.berkeley.edu

Technical Memorandum UCB/ERL M03/32 August 12, 2003

#### Abstract

This paper gives an overview of methods used for Design Space Exploration (DSE) at the system- and micro-architecture levels. The DSE problem is considered to be two orthogonal issues: (I) How could a single design point be evaluated, (II) how could the design space be covered during the exploration process? The latter question arises since an exhaustive exploration of the design space by evaluating every possible design point is usually prohibitive due to the sheer size of the design space. We therefore reveal trade-offs linked to the choice of appropriate evaluation and coverage methods. The designer has to balance the following issues: the accuracy of the evaluation, the time it takes to evaluate one design point (including the implementation of the evaluation model), the precision/granularity of the design space coverage, and last but not least the possibilities for automating the exploration process. We also list common representations of the design space and compare current system and micro-architecture level design frameworks. This review thus eases the choice of a decent exploration policy by providing a comprehensive survey and classification of recent related work. It is focused on System-on-a-Chip designs, particularly those used for network processors. These systems are heterogeneous in nature using multiple computation, communication, memory, and peripheral resources.

**Keywords:** Design space exploration, design space pruning, system-level design, micro-architecture design, design frameworks, benchmarking, multi-objective search.

#### Note

We focus on related work which applies methods in the context of design space exploration. Discussing the theory of optimization methods and the fundamentals of design evaluation is beyond the scope of this survey.

# Contents

| 1 | Motivation                                                 | 3  |

|---|------------------------------------------------------------|----|

| 2 | Introduction                                               | 5  |

| 3 | Methods for evaluating a single design point               | 7  |

|   | 3.1 Established benchmarks                                 | 8  |

|   | 3.2 Simulation-based evaluation                            | 8  |

|   | 3.3 Combination of simulation-based and analytical methods | 11 |

|   | 3.4 Purely analytical approaches                           | 11 |

| 4 | Methods for exploring the design space                     | 13 |

|   | 4.1 Optimization strategy                                  | 14 |

|   | 4.2 Objective/ cost functions and metrics                  | 16 |

|   | 4.3 Strategies for covering the design space               | 20 |

|   | 4.4 Pruning the design space                               | 23 |

|   | 4.5 Supporting functionality for automated DSE             | 26 |

| 5 | Representing the design space                              | 28 |

|   | 5.1 Architecture models                                    | 28 |

|   | 5.2 Application models                                     | 29 |

| 6 | Available Design frameworks for DSE                        | 32 |

|   | 6.1 System-level frameworks                                | 33 |

|   | 6.2 Micro-architecture centric frameworks                  | 35 |

|   | 6.3 Other frameworks                                       | 36 |

|   | 6.4 Comparison                                             | 37 |

| 7 | Trade-off analysis                                         | 38 |

| 8 | Benchmarking DSE approaches                                | 41 |

|   | 8.1 Indicators for comparing exploration algorithms        | 41 |

|   | 8.2 Defining DSE benchmarks                                | 43 |

| 9 | Summary and conclusion                                     | 44 |

#### 1 Motivation

Having a look at today's common practice to design an integrated circuit or a whole system we recognize the impact of the designer's experience gained in prior design projects on the final system architecture. Indeed, taking the application domain of network processing as a prominent example, we see quite a diversity of available architectures in order to implement the same kind of application [107]. This variety of designs can rather be explained by the knowledge gained in recently completed, prior designs in each of the design teams than by application-driven architecture decisions. That means, given a specification of the application and system requirements, the design team shrinks the range of feasible designs to a small number of possible designs by falling back on earlier, beneficial design decisions which might be sub-optimal for the current design problem and biased towards the designers' favored design style. The relative quality of the final design as a result of this ad-hoc system design approach compared to an optimal design will become even worse in the future due to the following trends:

- Increasing complexity of the design: The complexity of integrated circuits continues to follow Moore's law, thus doubling every 18 months. This in particular motivates to reuse prior design knowledge at higher levels of abstraction in order to cope with the sheer size of the design.

- Heterogeneous architectures: We see more and more heterogeneous architectures combining application-specific with general-purpose computing, different kinds of peripherals, and memory hierarchies. In addition, designers increasingly tend to use existing designs in parallel in order to fill the available area rather than to develop new and larger designs. Recognizing and exploiting the concurrency of applications therefore becomes a significant part of the design process. Besides this architectural diversity, more and more different technologies are being integrated onto a single chip, such as on-chip memory, analog interfaces, and high-frequency parts. It is therefore increasingly unlikely that a design team will be able to come up with an optimal solution by hand. Although a single designer could find an optimal subdesign of the overall system for his/her area of expertise (such as memories), naïvely putting optimal parts together does not necessarily lead to an optimal heterogeneous system.

- Deep submicron effects: A couple of effects which have been neglected during the design process in the past make the design quality worse, such as increasing interconnect delays and decreasing signal integrity. Again, this point underpins the growing dependency among different aspects of the design.

- Decreasing time to market: Last but not least the design window for success becomes smaller and smaller, thus increasing the pressure to reuse prior designs rather than developing new, optimized designs.

As a result of these tendencies we in addition discover that the development of software is often decoupled from the development of the hardware part if programmable parts are employed. A heterogeneous architecture as a result of ad-hoc integration of optimal subdesigns might therefore

turn out to be virtually impossible to program and configure. The performance of the software on the final hardware might thus not meet the requirements on the final hardware as expected.

We see the following approaches to partly release the designer from the constraints imposed by the mentioned trends:

- Programmable, application-specific architecture building blocks are increasingly used to replace ASICs, thus allowing their reuse for different application domains without sacrificing too much efficiency.

- Correct-by-construction methods, such as the automatic generation of a compiler from an architecture description language description, are employed to reduce the time needed for verification whether a design meets the specification.

- The development of software is introduced in an earlier phase of the overall design process. For instance, system-level design frameworks allow the modeling of the behavior of the software even at very abstract levels and retargetable compilers ease the evaluation of the actual software on the intended hardware at low levels of abstraction.

Although these techniques are able to relief the designer from complexity and time to market concerns to some extend, they are not sufficient to address increasing heterogeneity and a growing number of dependencies between subdesigns due to, for instance, deep submicron effects. As complexity increases, it is becoming more and more unlikely that an optimal design represents an 'intuitive' solution to the design challenge and it is therefore questionable whether an experienced designer could come up with a decent solution following the current ad-hoc design approach of pruning the design space by applying prior, favored design decisions. Consequently, a disciplined approach to design space exploration is needed in order to be able to evaluate large design spaces with a high number of potential designs. This includes algorithms to prune and cover the design space in a systematic way on different levels of abstraction and refinement. The goal of this paper therefore is to give a comprehensive survey and classification of recent work in the area of design space exploration of integrated circuits and systems to ease the choice of a problem-specific exploration policy. We compare the characteristics of different exploration methods and existing design tools. We also reveal areas of further research in order to improve the quantitative comparability of exploration techniques.

The paper is structured as follows. In the next section, we give an introduction to the problem of design space exploration. Section 3 continues with a discussion of methods for evaluating a single design point. In Section 4, a survey of approaches for traversing and covering the design space is given. In addition, techniques for design space pruning and automated exploration are reviewed. We give an overview of design representations used for DSE in Section 5 and summarize the properties of available frameworks in Section 6. Section 7 continues with a qualitative discussion of trade-offs involved by choosing appropriate evaluation and exploration methods. In Section 8 we suggest further steps to enable a more quantitative comparison of design space exploration algorithms. Section 9 concludes this paper.

### 2 Introduction

The term "design space exploration" has its origins in the context of logic synthesis. Clearly, a circuit can be made faster by spending more parallel gates for a given problem description (providing that the description offers enough parallelism) at the expense of area overhead. By extensively playing around with synthesis constraints, designer have been able to generate a delay-area trade-off curve in the design space defined by speed and area costs. This process of systematically altering design parameters has been recognized as an exploration of the design space.

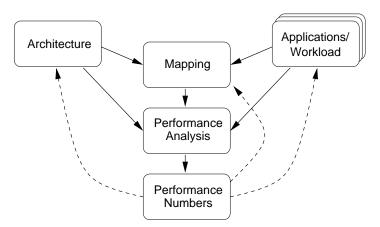

Scheme for automated design space exploration: Y-Chart. Design space exploration tasks today often deal with high-level synthesis problems, such as the automation of resource allocation, binding of computation and communication to resources, and scheduling of operations, for varying design constraints, given a fixed problem description. In order to support early design decisions and due to increasing design complexity, exploration tasks are more and more performed on the system level. A systematic exploration often follows the Y-chart approach [56], see Fig. 1, where one or several descriptions of the application (including workload, computation and communication tasks) and one architecture specification are kept separately. An explicit mapping step binds application tasks to architecture building blocks. The following evaluation of the mapping, e.g., in terms of performance, area, or power consumption may require synthesis steps of the architecture description, rewriting/adapting application code, and dedicated compilation phases of the application onto the architecture in order to evaluate the design and perform (possibly simulated) test runs. Constraints from the architecture, application, and workload descriptions may influence the evaluation. Results from the evaluation may trigger further iterations of the mapping by adapting the description of the application and workload, the specification and allocation (meaning the selection of architecture building blocks) of the architecture, or the mapping strategy itself.

Figure 1: Y-Chart approach to design space exploration.

In this paper we will in particular focus on two kinds of methods:

• Methods that deal with the evaluation of a single design, represented by the performance analysis step in the Y-chart.

• Methods for the coverage of the design space by (more or less) systematically modifying the mapping and the allocation of resources, corresponding to the feedback paths from the analysis to the mapping and architecture representations in the Y-chart.

Methods for covering the design space only alter the description of the application to adapt or refine the description according to the facilities of the allocated architecture building blocks in order to ease a feasible mapping. During a design space exploration run, the functionality of the application usually remains unchanged and only the workload imposed by the application may vary.

Evaluating designs. Methods for evaluating a single design range from purely analytical methods, which can be processed symbolically, to cycle-accurate and RTL-level simulations which need complex executable models of the design under evaluation. Before a design can be evaluated, compilation and synthesis steps may be required, e.g. the hardware part of the design may be synthesized on an FPGA-based prototype. The complexity of validation phases can be reduced by correct-by-construction synthesis steps that guarantee correct implementations of the specification, thus avoiding validation by, for instance, simulation of test stimuli. In this case, the system evaluation using stimuli can focus on extracting design characteristics only, such as resource utilizations.

Complexity of the exploration process. The solution space for a system-level design space exploration will quickly become large if arbitrary allocations and mappings are allowed. As a simple example, assume that b distinct hardware building blocks have been allocated and communication between these blocks is not a bottleneck. The application description may consist of t computation tasks. The building blocks are of a general-purpose type, such as CPUs with different micro-architectures. As a consequence, each task could potentially be mapped onto every hardware resource, leading to  $b^t$  feasible mapping choices. Thus, an exhaustive evaluation of all possible mappings quickly becomes intractable. Consequently, there is the need for automated and disciplined approaches to reveal a representative characterization of the design space without searching the design space extensively.

The complexity increases even further if multiple objectives are subject to the search. In order to evaluate one design whether it is Pareto-optimal (see Def. 4 in section 4.1) with respect to a set of solutions, all objective values of the design must exhaustively be compared with the corresponding objective values of every other design in the set. Fortunately, multi-objective explorations are usually bound to two or three objectives only, such as speed, costs, and power dissipation. The highest number of objectives that we found in related work is six [24].

It should be noted that exploration methods can work either on the problem space or the solution/objective space of the design. A system based on pre-designed IP-blocks can be optimized by, e.g., searching all possible combinations of parameters exported to the designer in the problem space, such as cache sizes and the clock frequency. Those parameters are part of the initial problem specification. In contrast to that, high-level synthesis methods are driven by constraints in the solution space, such as overall latency, power dissipation, and chip area.

**Def. 1 (Problem space)** The problem space is defined by properties of the system that do not represent immediate design objectives but rather natural characteristics of the design space. In the

context of DSE, the dimensions of the problem space often coincide with the axes of the architecture design space and may additionally include properties of the workload.

A memory architecture, for instance, could be described by the required number of cache levels, the sizes of each level, and the caching algorithm used. An application could be represented by a task graph and an event model that triggers the tasks. All these specifications are part of the problem description and do not give any insights into primary objectives, such as the speed of the system. An exploration algorithm working on the problem space thus systematically chooses a system configuration, evaluates it, and decides whether this configuration is feasible or not. Finally, an optimal solution is selected in terms of one or more primary objectives, such as speed.

**Def. 2 (Solution/objective space)** The solution space is defined by the primary objectives of the design space exploration, such as system cost, speed, and power dissipation.

An exploration algorithm working on the solution space systematically constrains feasible designs in terms of primary objectives (see Section 4.2), i.e., the algorithm has to determine whether a suitable design can be found that fulfills the constraints while optimizing other objectives. Design parameters in the problem space are chosen accordingly, e.g. by logic synthesis algorithms.

In the following sections, methods for evaluating and exploring the design space are reviewed in more detail.

# 3 Methods for evaluating a single design point

In this section methods used to evaluate a single design point are discussed. Related work shows a variety of different approaches from detailed cycle-accurate and RTL-level simulations to purely analytical methods on relatively high abstraction levels. Depending on the chosen evaluation method, the mapping step in the Y-chart [56] (see Fig. 1) to determine performance values can be fairly complex involving explicit compiling or synthesis phases, whereas other methods represent mapping decisions implicitly by varying parameter sets. The orthogonal problem how to traverse the design space, given performance results for individual design points, will be discussed in the subsequent section.

Simulation-based evaluation can only estimate a single stimulus setting at a time, representing one particular implementation of a problem specification. The simulated workload must be chosen by the designer in a way that it represents a variety of typical working scenarios to avoid the optimization of the design for a special case. Analytical methods can help here since they are able to evaluate a design for a class of workloads (representing a range of stimuli for simulation-based tools) in a single pass. One drawback of analytical approaches however is that they often provide less precise results than simulation. Both evaluation techniques require a defined set of 'experimental' setups in order to produce performance-indicative, representative, reproducible, and comparable results during an exploration run. This procedure is often called benchmarking and is elaborated in the next subsection. Simulation-based and analytical methods for evaluating a design point are summarized in the following subsections.

#### 3.1 Established benchmarks

In order to determine meaningful and comparable performance values, all evaluation methods need defined benchmarks of some kind to describe the workload imposed on the design under evaluation. In order to determine reproducible results, a benchmark includes a description of the application, a description of the architecture under test, constraints on the workload (e.g. defined by the working environment of the (embedded) system), a feasible mapping of the application onto the architecture, and defined metrics and cost functions. Available benchmarks can be classified according to their application domain. Examples are:

- Network processing: Related work on defining benchmarks for network processors include CommBench [123], NetBench [77], and activities of the Network Processor Forum (NPF, http://www.npforum.org). Related work on disciplined approaches for evaluating network processors can be found in [117, 20]. The Internet Engineering Task Force (IETF) has a work group on benchmarking methodologies (BMWG) of internetworking technologies.

- General purpose computing: Benchmarks for general-purpose and scientific computing are published by the Standard Performance Evaluation Corp. (SPEC, http://www.spec.org). The Business Applications Performance Corporation (BAPCo, http://www.bapco.com) focuses on benchmarks for personal computers and notebooks.

- Embedded systems: Benchmarks for embedded systems including automotive, telecommunication, consumer, and control systems can be found in MiBench [44] and are also defined by the Embedded Microprocessor Benchmark Consortium (EEMBC, http://www.eembc.org).

- Multimedia-centric computing: Benchmarks focusing on multi-media processing can be found in MediaBench [67] and in the DSP-centric BDTI benchmarks from Berkeley Design Technology, Inc.

- Database and transaction processing: Business-oriented transactional server benchmarks are defined by the Transaction Processing Performance Council (TPC, http://www.tpc.org). SPECjAppServer2002 is a client/server benchmark from SPEC for measuring the performance of Java enterprise application servers in end-to-end web applications.

- Parallel Computing: Examples of benchmarks for parallel computing and multi-processing are PARallel Kernels and BENCHmarks (Parkbench, http://www.netlib.org/parkbench), Stanford Parallel Applications for Shared Memory (SPLASH2 [124]), and SPEC OMP (OpenMP Benchmark Suite).

#### 3.2 Simulation-based evaluation

Simulation means to execute a model of the system under evaluation with a defined set of stimuli. A simulation can therefore only trace certain execution paths in the state space of the system that (hopefully) represent typical working modes of the design. Simulations are particularly well suited to investigate dynamic and sporadic, unforeseeable effects in the system, whereas formally verifiable systems require a deterministic behavior, given any stimuli. Results from analytical models can be too pessimistic since these models often consider the worst-case. Simulations may

reveal more realistic results for average-case optimization. One drawback of simulations is the need for an executable model. In an early phase of the design providing such a model may impose an unsubstantiated burden for evaluating early design decisions.

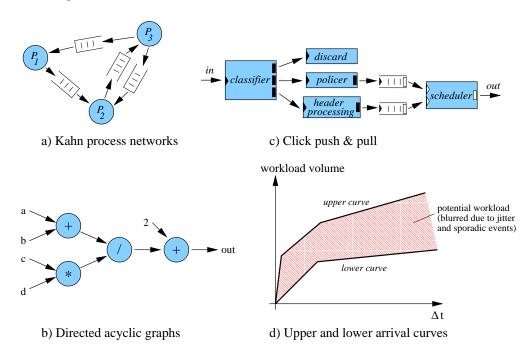

**System-level simulation.** The Ptolemy framework [68] (http://ptolemy.eecs.berkeley.edu) can be used to model and simulate the interaction of concurrent system components by using different models of computation (MoC). Through hierarchical composition and refinement the designer is able to specify software and hardware behavior at various levels of abstraction using different MoCs which are most suitable for the corresponding application domains.

Lieverse et al. [74] present an architecture exploration method based on a single MoC, namely Kahn process networks. The functional behavior of an application is kept separately from models describing the timing behavior of the architecture (e.g. CPU cores and buses). Applications are annotated with the computational requirement of one event. On the appearance of a computation event, the corresponding computation demand can be recorded in an execution trace. In the actual implementation of the tool traces are not recorded, but event demands are directly passed on to architecture models that associate a defined latency with each of these events. The actual assignment of computation events to architectural models determines a mapping of application processes to architecture components. The Artemis work described in [96, 95] refines the work described in [74] in order to resolve deadlocks in Kahn process networks by introducing the concept of virtual processors and bounded buffers. One drawback of restricting the designer to using Kahn process networks is the inability to model time-dependent behavior. Moreover, since all scheduling decisions are implicitly taken following the organization of FIFO buffers, all resources are assumed to use FCFS schedulers on the event granularity level.

Thus, a natural alteration is used in [39] to model time-dependent workloads of network processors. Here, process networks with a notion of time are employed not only to model backlog in packet queues due to limited capacity of resources and the burstiness of packet arrivals but also to implement sophisticated, time-dependent schedulers, such as Weighted Fair Queueing (WFQ). One further benefit of a notion of time is the option to investigate trading off the response time of a network processor versus the processing capabilities (i.e. resource load) of its computing resources by varying the length of loss-free event queues in front of schedulers.

Computation demands used as annotations for events could be determined by estimation, pseudo-code analysis, or even by isolated, fine-grained simulations of individual tasks to increase the accuracy at the system-level as, for instance, described in [6] and [83].

Cycle-accurate simulation. In order to increase the accuracy of evaluating a design, an often used level of refinement is defined by the precision of a single clock cycle. Hardware models at this level of abstraction can either be based on software, modeling the timing and behavior of the hardware, or actual hardware descriptions in a hardware description language, enabling rapid prototyping on, for instance, an FPGA. The corresponding application under evaluation often is the actual application itself, i.e., it is described in a high level programming language or assembler, and not by a functional or behavioral model of the software. A cycle-accurate evaluation thus comprises either a co-simulation of the application together with the hardware description on a hardware simulator or an integrated simulation of the application on a software model of the hardware.

The Open SystemC [43] Initiative (OSCI, http://www.systemc.org) tries to leverage design knowledge in the C and C++ programming languages for system level modeling and evaluation. The goal is to provide an executable specification of hardware, software, and communication parts of a design early in the design process and to establish a path of refinements towards implementation, thus bridging the gap in current design practice between high-level models and hardware description languages. SystemC allows several layers of refinement and introduces notions of components (called modules), communication channels, hierarchical composition, processes, events and signals as well as hardware-oriented data types – for instance bit level and logic types – in order to express concurrency, structural descriptions, communication, and synchronization. Future versions of SystemC will also incorporate primitives to express real-time operating system functionality and schedulers. SystemC's simulation library supports cycle-accurate evaluation. SpecC [16] also supports the iterative refinement of a design and is based on the C language. SpecC is an extension of C with additional hardware and software modeling constructs, whereas SystemC is a C++ class library. A detailed comparison of the capabilities of SystemC and SpecC can be found in [17]. Together with the richness of the C and C++ languages however also comes the potential drawback of versatility of implementations. That means, for instance, that SystemC models are not necessarily synthesizable. Support for SystemC has been integrated into a variety of tool flows, such as Synopsys' CoCentric System Studio, Axys Design's MaxSim Developer Suite, CoWare's N2C, and Cadence's Signal Processing Worksystem (SPW).

Micro-architecture features of programmable processors are often investigated using cycleaccurate software models. Simulators, such as SimpleScalar [15] and SimOS [101], are specialized in certain classes of CPUs, such as MIPS-based cores. Variations of the micro-architecture that only affect run-time mechanisms, such as caches, branch predictors, and issue widths, can be explored without the need of recompiling the application. Such a simulator therefore remodels a fixed IP-core, where only a small set of design parameters is exported to the user, such as the cache size. Modifications that affect the instruction set or variations of the data path however require a retargetable compiler that needs to compile every application to all potential micro-architectures. These mapping and modification steps may be eased and automated using architecture description languages (ADLs). One of these ADL-based design environments is being developed in the Mescal project [78, 121]. Another example of ADL-based architecture exploration is described in the work of Mishra et al. [81, 80, 82] based on the EXPRESSION language [45]. Further examples of ADLs are LISA [92], nML [28], and MIMOLA [69]. ADLs can be distinguished according to the family of architectures they are able to express (e.g. single vs. multi-threaded), the ability to integrate effects of the micro-architecture (e.g. pipelining), and their options to support automated design space exploration by, for instance, an explicit mapping step and support for retargetable code, simulators, and synthesizable hardware generation. ADL-based frameworks often allow the automatic generation of cycle-accurate software models of the hardware and also partly support the automatic creation of synthesizable hardware descriptions. Surveys of ADLs can be found in [97, 116].

Examples of retargetable compilers – a prerequisite for automatic, cycle-accurate design space exploration of processor micro-architectures – targeted at embedded systems [70] and ASIPs are CoWare's LISATek (http://www.coware.com) [49], Chess/Checkers (http://www.retarget.com) [65], Tensilica's XCC (http://www.tensilica.com), and FlexWare [72]. These compilers in particular specialize on code density, power issues, and reliability.

## 3.3 Combination of simulation-based and analytical methods

In order to reduce the overhead involved with the simulation of a complete system under evaluation, the following methods try to reduce simulation time by gathering all characteristics, which are common between designs being evaluated and which are not subject to the design space exploration, into a single initial simulation. Information extracted from the initial simulation run can be reused by all evaluations. The evaluation time narrows to the time it takes to evaluate distinctive features.

Trace-based performance analysis. This kind of performance estimation is in particular common for evaluating cache and memory structures, see the survey in [118]. An initial program run extracts all memory accesses and stores them in a trace. Given a cache model, the trace can then be used to calculate hit and miss statistics as well as overall performance estimates. The aim of this procedure is to save evaluation time by only doing an expensive simulation once. Different cache structures can be evaluated by reusing the same trace data collected from the initial simulation. Exemplary studies and tools that use this method for performance and energy analysis driving the design space exploration of a memory subsystem are by Fornaciari et al. [30, 31] and Givargis et al. [36].

In the work presented by Lahiri et al. [64, 62, 63] this technique is applied to the design of on-chip communication structures. An initial system-level simulation of communicating components representing the workload environment, i.e. HW and SW components surrounding the communication structure under investigation, is performed to collect traces of communications going on between components. Traces are compressed by generating a communication analysis graph (CAG) that accumulates burst transfers and computations into single events. Given a communication substructure template consisting of point-to-point and shared connections as well as bridges, the CAG is modified to incorporate effects of synchronization, arbitration, and block transfers. Modifications include adding nodes and adjusting time stamps of nodes, which enables the estimation of performance and resource utilization.

Zivkovic et al. [128] augment traditional traces, that usually contain information on data transfers and task executions only, with control information in order to evaluate the cost of control as well.

Analytical models with initial, calibrating simulation. The analytical approach described by Franklin and Wolf [32] requires an initial characterization of benchmarks using exhaustive simulation runs for a range of cache organizations. Extracted information from these runs like miss rates and load and store instruction shares are fed into analytical models which allow reasoning about resource utilization, area requirements, and performance. The approach has been extended in [33] to include power requirements.

#### 3.4 Purely analytical approaches

Analytical methods come into play if deterministic or worst-case behavior is a reasonable assumption for the system under evaluation. In addition, building an executable model of the system as

well as simulations might be too costly or even impossible at the time of the evaluation. Analytical models thus in particular ease early design decisions by identifying corner cases of potential designs.

**Static profiling.** Well established methods for static program analysis, such as the complexity analysis of algorithms, the dependency analysis of a static schedule of a task or function call graph to extract worst-case behavior, or simply counting of operations appearing in pseudo code, can be used for performance estimations of an application mapped onto an architecture, as for instance performed in [40]. The reader is referred to standard literature in Computer Science, such as books by Knuth [58] and Sedgewick [105], to learn more about complexity analysis and common data structures for established sorting and searching algorithms. Analytical approaches that take certain elements of the micro-architecture of a programmable processing core into account can be found in the domain of worst-case execution time (WCET) estimation for embedded systems. The application models usually require the absence of sporadic and non-deterministic effects, such as the presence of interrupts, recursion, and operating systems. The analysis works on assembler, pseudo-code, or a high-level programming language description and therefore often has to neglect the impact of certain compiler optimizations. The architecture description is bounded to a single processor with simple pipeline and cache models. The formulation as an integer linear program often constitutes the core of the analysis as, for instance, described in the papers by Li et al. [71] and Theiling et al. [112].

Event stream-based analytical models. For certain application domains dedicated calculi, task, and workload models exist which allow symbolic evaluation of a design. Richter et al. [99] (and the references therein) give an overview of mature analytical techniques for evaluating the task execution on shared resources for event streams, such as periodic events, periodic with jitter, and sporadic preemptions. They extend these techniques by coupling the analytical models using event model interfaces, thus enabling system-level evaluations of platform-based designs. If coupling existing analytical models is not a concern, calculi provide a generalized approach to real-time embedded system design, potentially providing tighter bounds to end-to-end delays and storage bounds of shared memory implementations. One example is the network calculus [66] which has been applied to network processor design [113, 115, 42] and used for evaluating real designs [41, 19]. Its applicability has also been shown for real-time embedded systems in general [18].

High-level synthesis. The evaluation of an application-specific architecture given a task graph may require an explicit synthesis step in order to extract area requirements and detailed timing information. The classical high-level synthesis problems of allocating resources, binding computations to resources, and scheduling operations under timing and/or resource constraints are either solved by exact methods, such as integer/mixed linear program formulations [12, 103], or by heuristics, such as ASAP and ALAP [13, 98], list- [10, 21, 1], force-directed scheduling [26, 25], or evolutionary algorithms [10, 25] (mainly used for allocation and binding problems).

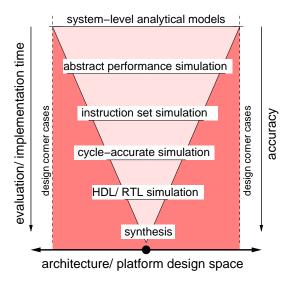

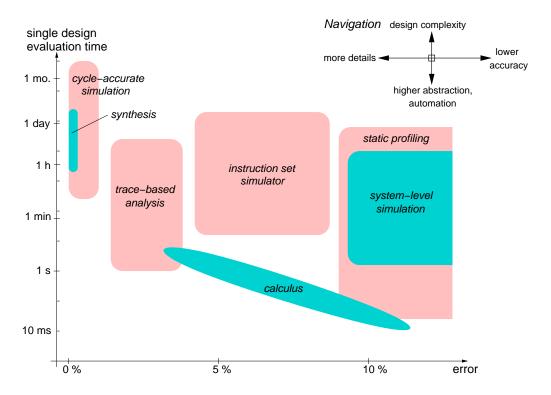

In conclusion, the trade-offs involved by choosing an appropriate evaluation method are shown

in Fig. 2. Analytical models allow a fast evaluation of a relatively large fraction of the design space, thus enabling the identification of corner cases of the design. Over several possible steps of refinement with increasing effort for evaluation and implementation the design space can be bound to one particular design point. This funnel representation resembles the upper part of the platform-based design double pyramid [29], i.e., the final design point could also represent a whole platform. Methods for systematically exploring the design space on one of the layers of abstraction are discussed in the following section.

Figure 2: Design funnel model. Refinements of the evaluation method narrow the reachable design space (vertical direction), whereas covering algorithms explore the size of the design space (horizontal direction).

# 4 Methods for exploring the design space

After having discussed methods used to evaluate a single design point, this section provides a survey of algorithms used to walk through and reasonably cover the design space. Exploring the design space is an iterative process which is usually based on the Y-chart [56] approach. Here, application and architecture descriptions are explicitly associated to each other in a mapping step and evaluated afterwards. The mapping could include compile and synthesis phases to enable the performance analysis. Results from the evaluation of that particular design point could then be used to further guide the exploration by varying application and architecture descriptions as well as the mapping between the two.

In the following sections we provide a coarse classification of search strategies depending on the number of objectives that are active during the exploration, a review of common cost functions and metrics, a survey of recent work on search strategies and design space pruning techniques, and a list of supporting functions for automated exploration in the area of computer architecture design.

## 4.1 Optimization strategy

For the classification of methods we need the term of Pareto optimality [88] which is introduced next. This property only has a meaning if a multi-objective search of the design space is performed. In the area of micro-architecture design, objectives could be the minimization of costs, power consumption, or the maximization of the speed. These objectives may show tight connections between each other. Thus, optimizing with a single objective in mind may reveal severe trade-offs with respect to the other objectives.

**Def. 3 (Pareto criterion for dominance)** Given k objectives to be minimized without loss of generality and two solutions (designs) A and B with values  $(a_0, a_1, \ldots, a_{k-1})$  and  $(b_0, b_1, \ldots, b_{k-1})$  for all objectives, respectively, solution A dominates solution B if and only if

$$\forall_{0 \le i < k} i : a_i \le b_i \quad and \quad \exists j : a_j < b_j .$$

That means, a superior solution is at least better in one objective while being at least the same in all other objectives. A more rigorous definition of *strict dominance* requires A to be better in all objectives compared to B, whereas the less strong definition of *weak dominance* only requires the condition  $\forall_{0 \le i \le k} i : a_i \le b_i$ .

**Def. 4 (Pareto-optimal solution)** A solution is called Pareto-optimal if it is not dominated by any other solution. Non-dominated solutions form a Pareto-optimal set in which neither of the solutions is dominated by any other solution in the set.

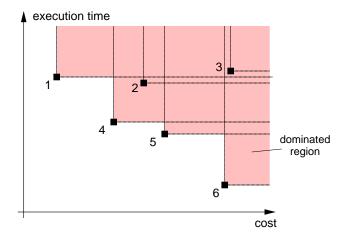

That means, designs in the Pareto-optimal set cannot be ordered using Def. 3. Thus, all elements in the set define reasonable solutions and they are subject to further decision constraints in order to choose a design for a given problem. An example is visualized in Fig. 3. The two-dimensional design space is defined by cost and execution time of a design, both to be minimized. Six designs are marked together with the region of the design space that they dominate. Designs 1, 4, 5, and 6 are Pareto-optimal designs, whereas design 2 is dominated by design 4 and design 3 by all other designs, respectively. Without further insights into the design problem all designs in the set  $\{1,4,5,6\}$  represent reasonable solutions.

Optimization methods can now be classified according to the following criteria (see [50] and the references therein):

• Decision making before search: The designer decides how to aggregate different objectives into a single objective (cost) function before the actual search is performed. In this way, well-established optimization methods can be applied. However, e.g. by using a weighted sum of objectives, certain regions of the design space may no longer be reachable by the search method (see the example below). Another procedure would be to convert certain objectives into constraints for an optimization problem with a reduced number of objectives. A non-arbitrary aggregation of objectives requires some knowledge about the design space to find a solution which is not sub-optimal. This might be inconsistent with one of the major goals of DSE, i.e. the determination of characteristics of the design space.

Figure 3: Two-dimensional design space with Pareto-optimal designs 1, 4, 5, and 6.

- Search before decision making: The search for optimal solutions is performed with multiple objectives in mind which are kept separate during the search. The result of the search is a set of Pareto-optimal solutions. Only after the search additional criteria or preferences are applied to find an optimal solution for a given problem. In this way an unbiased search can be done and problem-specific decisions only require the set of solutions. Hence, a single search may serve several problem-specific decisions (no rerun of the search required).

- Decision making during search: This category is a mixture of the two preceding groups. Here, initial search steps may be used to further constrain the design space and/or guide the search to certain regions of the design space. These steps may be repeated iteratively. Constraints and/ or guidance can be derived automatically or interactively by presenting intermediate search results to the designer.

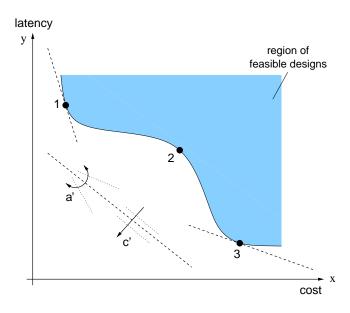

Thus, the choice of a single- or a multi-objective search algorithm not only influences the point of time when design objectives are defined, but also affects the whole exploration process. Using a single-objective search, the result of the optimization is a single design point. That means, searches must be repeated with, for instance, varying weights or constraints on the objective function in order to explore the design space and generate a set of Pareto-optimal solutions. Depending on the shape of the objective function that aggregates several objectives, certain regions of the design space might not be reachable at all. In the example in Fig. 4 the region of feasible solutions in the design space defined by cost and latency is shaded. Designs one, two, and three represent possible Pareto-optimal solutions. Assume that a weighted sum of the objectives x and y is used as the objective function f, i.e.

$$f(x,y) = a \cdot x + b \cdot y \qquad a, b \in \mathbb{R}_0^+ \tag{1}$$

with some weights a and b. The overall goal is to minimize f, i.e.

$$c \stackrel{!}{=} f(x,y)|_{min}$$

Equation 1 can be transformed to

$$y = \frac{c}{b} - \frac{a}{b} \cdot x =: c' - a' \cdot x$$

and describes a straight line in x-y space. As we can see in Fig. 4, the ratio of the weights a and b therefore defines the constant slope of the line, whereas the optimization goal to minimize f moves the line towards the origin. Two different optimization runs are shown where we were able to find the solutions one and three. It is clear from the picture that we will never be able to reach solution two with any combination of the weights a and b since the straight line will always hit the solutions one or three in order to minimize f (represented by c). In a similar fashion one can also graphically show that the reduction of objectives by converting objectives into constraints in fact reduces the reachable space of solutions.

Figure 4: Finding Pareto-optimal designs using a weighted sum of objectives.

Contrary to that, multi-objective searches are potentially able to find all three Pareto-optimal solutions in a single optimization run. The actual choice for one of the solutions depends on further constraints or objective functions that apply combinations of the objectives used for the search. A typical application scenario could be the exploration of an IP-core library in terms of, for instance, cost and performance for a certain application domain. Suitable solutions depending on the actual application could be the fastest solution, the cheapest solution or the solution with the best cost/performance ratio. All three solutions can be derived from the set of Pareto-optimal solutions without rerunning the search.

### 4.2 Objective/cost functions and metrics

In the following, widely-used objectives for design space exploration are pointed out. Singleobjective optimizers tend to use a weighted sum, ratio, or product of several objectives in order to consider conflicting criteria, whereas multi-objective algorithms can keep objectives separately so that the results of the search are not biased towards a certain region of the design space.

#### 4.2.1 Primary objectives

Primary objectives concern the properties of the overall system and are typically used directly as optimization goal, i.e., they do not represent an intermediate, supportive cost metric, but drive the optimization process directly. The objectives listed in this category can universally be applied to design space exploration and are not domain-specific.

- Cost: The cost of a design could be measured as the sum of all component costs integrated in the system, e.g., based on the wholesale prices from different component manufacturers or based on the own manufacturing costs which could, for instance, be determined by the area consumption in the target technology and the packaging costs. Fixed costs, such as the fabrication costs (e.g. mask sets) or the engineering costs for designing the system, cannot drive the optimization process and are therefore often not included.

- Power dissipation: Optimization for power more and more becomes the focus for design space exploration. On the one hand, high-end systems optimized for speed have to cope with the generation of heat within the system that degrades the life-time of the components. On the other hand, embedded systems not only focus on the minimization of the worst-case power dissipation, but also on the power leakage during idle periods of the system in order to decrease the costs for maintenance, e.g., by extending the life-time of batteries.

- Speed: The speed of a design can be expressed by different metrics, such as the throughput achieved for computations and communications, the overall amount of data processed or transferred, the latency/ response time for certain events (whether deadlines are met), the period length of a schedule of computations and communications, or the bare clock speed supported by the design.

- Flexibility: The flexibility of a design can be seen as a meta-objective since it is difficult to express this metric quantitatively. However, many fundamental design decisions are based on the need of programmability or dynamic reconfigurability in order to extend the life-time of a design, to be able to incorporate late fixes due to, for instance, changes in communication standards, or to ease the remote maintenance of an embedded system. A first step towards defining quantitative metrics for flexibility can be found in the work by Haubelt et al. [47]. An application is described as a hierarchical DAG where hierarchy levels represent different options (algorithms) to implement the same functionality denoted by the parent node in the graph. An architecture is supposed to be more flexible the more options described in the application DAG it can implement, given timing and cost constraints. This definition of flexibility however requires that all possible functionality of the application can be enumerated in advance. Often, flexible architectures are however used in order to be able to implement functionality unknown at design time. In order to determine an upper bound on flexibility with this definition, the flexibility of a programmable architecture would only be bounded by the memory space restricting the number of possible programs.

#### 4.2.2 Secondary objectives

Metrics in this category are either focused on the properties of only a part of the overall design or provide supportive information on the design, i.e., they reveal characteristics of the design that influence primary goals. The utilization of resources, for instance, could be seen as one component of the primary cost or power dissipation objectives. Secondary objectives are often problem-specific and facilitate the analysis of the overall design, pointing the designer to bottlenecks of the design. Metrics listed under primary objectives could, of course, also be applied to only parts of the design in order to support the analysis of the system. It should be noted that there are also optimizer-specific metrics that guide the search, such as the steepness to surrounding solutions in the case of hill climbing or the number of dominated solutions in the case of some multi-objective, evolutionary algorithms. The discussion of optimizer-specific metrics is beyond the scope of this paper. Common secondary objectives are:

- Utilization of computation and communication resources: The utilization of a resource determines the fraction of the overall execution time of a benchmark during which the resource is busy with processing the benchmark. Depending on the primary goal and the application domain, the goal of the optimization could be to maximize the utilization in order to exploit the silicon area as much as possible. Reducing the utilization however could lead to more power-efficient solutions that could also provide headroom on flexible architectures for further extensions of the application.

- Static/dynamic profiling results: Given an executable specification of the application, different kinds of profiling information could be extracted to guide further design decisions. An example is generating a histogram of the instructions used, e.g. data transfer vs. control vs. computation vs. bit level operations, that could indicate further exploration steps towards certain architectures supporting the most frequent operations in hardware. Profiling results could therefore be used as an affinity metrics towards certain design decisions.

- Affinity metrics: Affinity metrics defined by Sciuto et al. [104] determine whether an executable specification of the application favors DSP-, ASIC-, or general purpose-like computing solutions as architecture component. Exemplary metrics are the multiply-accumulate degree, I/O ratio, and bit manipulation rate of the reference application.

- HW-SW partitioning specific metrics: Metrics in the domain of hardware-software partitioning can be seen as a special case of affinity metrics with two design choices only. For a given problem description it must be decided which parts of the specification should be implemented in software and which in hardware. Indicators, such as potential speedups, area-and communication overheads, locality and regularity of computations as, for instance, defined in [93, 21], are used for guiding the decision towards hardware or software.

- I/O- and communication-specific metrics: Apart from primary speed objectives, such as throughput, latency, and the number of transactions, I/O-specific metrics include the number of I/O stall cycles and arbitration penalties which affect the primary speed metrics.

- Memory-specific metrics: Cache characteristics that in particular represent the speed of the memory subsystem for a given application include the number of conflict and capacity misses,

cache hit and miss ratios, as well as the locality of accesses extracted from the application. Metrics reflecting cost and power dissipation properties are the code size and the memory consumption of the application, e.g., generated from the maximum processing backlog of a task graph.

- Reliability: In the domain of embedded systems reliability may become as important as cost and power dissipation objectives since it might be virtually impossible to service the remote system or since hard real-time functionality must be preserved under all circumstances. Reliability comes at the price of over-provisioned and/or redundant designs.

- Deterministic behavior: In the domain of hard real-time systems, deterministic behavior might be a primary objective in order to fulfill safety requirements. Deterministic behavior is achieved by dimensioning the design for the worst-case behavior of the system. All dynamic and sporadic events must only have bounded effects on the design, i.e., the behavior must be predictable.

- *Physical size:* The physical size and weight of a design may be of primary importance for embedded systems in, for instance, the automotive domain and particularly affects the cost of the design.

- Compatibility: In order to partly retain the investment in previous designs, the compatibility of software, or the computing infrastructure to the new design becomes important. For the hardware part of the new design this could mean to maintain a constant interface to the surrounding computing environment, whereas compatible software requires a constant programming model for the user. That means, compatibility usually comes at the price of suboptimal cost and/ or power dissipation objectives.

- *Usability:* Usability describes the ability of a design to ease its initialization, configuration, and programming towards the deployment in a certain application domain. Usability could also include the properties of the user interface.

- Testability: The support for testing a circuit can be a considerable cost factor of the design. Hardware building blocks must be included or adapted to allow a test of the circuit using externally generated test vectors. Partial or full scans must be supported by test points and scanable registers and might also require the support of certain standardized test modes, such as JTAG boundary scan. A system can also provide circuitry to generate test vectors internally, which is called built-in self test.

#### 4.2.3 Combined metrics

In particular single-objective optimizers combine several objectives in order to consider conflicting criteria. Multi-objective algorithms could essentially also use combined objectives in order to reduce the number of dimensions to the problem, i.e., it could make sense to only consider the speed-cost and the flexibility-cost ratios for a certain design and not speed, cost, and flexibility as separate optimization goals. The most prevalent combined objectives are:

- Energy-delay product: The energy-delay product is in particular used to assess embedded systems. The power requirements are trade off against the speed of the design with the overall objective to reduce the product.

- Computations-power ratio: This objective can be interpreted as a computational density related to power dissipation. Designs are supposed to be better than others if they achieve more computations for a given power budget or consume less power for a given speed. The ratio between the number of computations and the power dissipation for a defined benchmark reflects this.

- Speed-cost ratio: This combined objective represents a computational density related to the costs of the design. A design is better than other designs if it achieves higher speed at the same price or the same speed at a lower price. The ratio between the speed of a design and its cost combines this behavior in a single objective.

- Flexibility-related: In the same way the performance of a design has been combined with cost and power objectives in the preceding combined objectives, ratios and products can be defined to express the trade-off between flexibility and cost, speed, or power. Examples are the flexibility-power ratio, the flexibility-cost ratio or the flexibility-delay product.

In the following, we review methods for exploring the design space that can be employed having a single or multiple primary objectives in mind.

# 4.3 Strategies for covering the design space

In this subsection, related work concerning the question how one could cover the design space is discussed. The mentioned categories are not strictly orthogonal to each other. In the following Subsection 4.4 methods for reducing the size of the design space are revealed that can be used in combination with any of the approaches presented in this subsection in order to decrease the exploration time.

Exhaustively evaluating every possible design point. This straightforward approach evaluates every possible combination of design parameters and therefore is prohibitive for large design spaces. The design space can be reduced by limiting the range of parameters and/or by parameter quantization. Multiple objectives can easily be maintained. The search process is completely unguided and unbiased towards preferences of the designer. Examples of design systems and case studies based on exhaustive search include system-level simulation [39, 6, 125], high-level synthesis [11, 13, 22, 4, 26, 111, 103], ADL-driven approaches [80, 91], cycle-accurate simulations [57, 48], instruction set simulators [36], code parallelization and partitioning onto multi-processors [54], trace-based analysis [64], and last but not least static analysis [40].

Randomly sampling the design space. Evaluating only random samples is the obvious choice for coping with large design spaces. It also has the advantage of revealing an unbiased view of the characteristics of the design space. In [14], a Monte Carlo-based system is described where random samples of the solution space are generated by randomly creating constraints for logic

synthesis. Another approach is to apply simulated annealing techniques. Starting from an initial design, changes to the design become more and more unlikely with advancing search time. In [110], Srinivasan et al. compare explorations driven by simulated annealing with results using an evolutionary approach. Gajski et al. [34] combine an exhaustive search over all possible architecture allocations with a simulated annealing-based exploration of mappings for each allocation.

One could also think of combining the mentioned random walks with principles from Tabu search [38] in order to avoid evaluating the same design twice. Tabu search thus enforces diversification into unexplored regions of the design space and also incorporates mechanisms to explore around interesting design points found so far (the so-called intensification phase of the search). Tabu search however would require additional, possibly computational intensive maintenance operations in order to keep track of recent moves and bad strategic choices. Tabu search has its roots in operations research and has only seldom been applied to electronics design so far. We are not aware of any related work using Tabu search in the context of electronics design. Moya et al. [84] compare Tabu search with simulated annealing for an artificial, two dimensional optimization scenario. Tabu search appears to be more robust against discontinuities and errors in the cost function and more effectively covers "bumpy" terrain than simulated annealing. Tabu search is also the more promising search strategy compared with simulated annealing in the architecture allocation problem investigated in [5].

Incorporating knowledge of the design space. Search strategies in this category try to improve the convergence behavior towards (Pareto-) optimal solutions by incorporating knowledge of characteristics of the design space into the search process. The knowledge may be updated with every iteration of the search process or may be an inherent characteristic of the search algorithm itself. All mentioned methods are heuristics.

Hill climbing, for instance, evaluates the neighborhood of the current design to determine the steepest next step towards the optimization goal. In order to avoid being trapped on top of a local maximum, hill climbing requires backtracking mechanisms which might be expensive in "bumpy terrains". Moreover, the search becomes aimless on plains and is not able to recognize diagonal ridges since the probe directions would always lead to lower quality solutions. In [62], hill climbing is used to explore the mapping of communication onto channels. In [109], a kind of hill climbing is one of the investigated techniques to explore VLIW micro-architectures.

Evolutionary search algorithms combine random walk with survival-of-the-fittest ideas while constructing new generations of a set (population) of solutions. Better solutions are more likely to survive from generation to generation and new solutions can be either created by mutation (random walk) or crossover of existing solutions. Crossover tries to combine features from two good solutions to generate even better solutions. In the way the designer chooses a representation of the problem and implements the mutation and crossover operations (working on those representations) already guides the search. For instance, mutation and crossover operations may generate new solutions that are not feasible. A repair mechanism could then prefer certain features of the solution over others. Thus, domain knowledge may inherently guide the search. Naïve implementations of those operations may however also avoid certain regions of the design space to be reached. Moreover, problem-specific representations require recoding of the evolutionary operations for other problem domains. Single-objective evolutionary algorithms have been used in [110, 1] and multi-objective evolutionary searches are described in [113, 10, 87, 2, 3, 24, 25].

Dick et al. [25] combine an evolutionary search with simulated annealing so that allocation and binding changes are less likely to happen with an increasing number of iterations.

Searches may also iteratively be guided by distance measures or other means of affinity towards certain regions of the design space. Sciuto et al. [104] define affinity metrics for applications towards mappings onto DSPs, ASICs, and general-purpose processors. Peixoto et al. [93] define metrics which favor resource sharing. Those metrics guide optimizations towards clusters of similar computations that show high locality. In this way, the communication between clusters is minimized, whereas resource sharing is maximized.

Path-oriented versus unguided search. This distinction emphasizes how the search progresses from iteration to iteration. Path-oriented searches are, for instance, hill climbing and evolutionary algorithms (implementing crossover). Exhaustive searches and random samples like unsupervised Monte Carlo methods belong to the class of unguided searches. Again, the latter class aims to give an unbiased view of the design space, whereas algorithms from the former class use domain knowledge of the design space to guide the search. Path-oriented walks may have the advantage of potentially reusing intermediate results of earlier design evaluations along the path. The underlying assumption here is that a design only slightly changes from one step to the next so that most of the evaluation experience from the previous design can be reused for the evaluation of the current design.

Single design at a time versus set-oriented search. This property differentiates between the number of designs that must be kept available in each iteration to perform the search. Exhaustive searches and random walks only look at one solution at a time, whereas methods exploiting domain-specific knowledge tend to use several designs at a time to find an improved design. Hill climbing and evolutionary algorithms thus belong to the latter category.

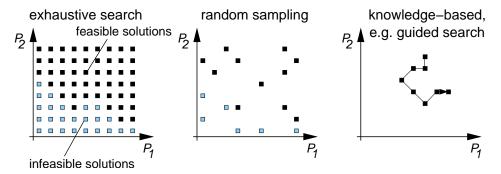

In summary, Fig. 5 graphically describes different search strategies for covering the design space. A discrete design space defined by two design parameters (in problem space) or two design constraints (in solution space)  $P_1$ ,  $P_2$  is assumed. Otherwise, an exhaustive search would already constitute a subsampling of the design space in this figure, since the parameters would have been quantized before the search.

Figure 5: Common approaches for covering the design space. A discrete, two-dimensional design space defined by two design parameters/ constraints  $P_1$  and  $P_2$  is shown.

# 4.4 Pruning the design space

All mentioned exploration methods can employ further techniques to reduce the complexity of the search by pruning the design space. Several practical approaches have been described in the literature, as will be described next.

**Hierarchical exploration.** Starting with a coarse problem statement interesting regions of the design space are identified and ranked. Refined models are used to explore those regions. The higher-level models could also be back-annotated with results from the refined explorations to improve the high-level characterization of the design space. The search thus switches back and forth between high- and low-level explorations.

Hekstra et al. [48] use a single simulation and profiling run of an exemplary VLIW architecture to extract timing information for all possible VLIW designs of their architecture library. Corner cases of the design are simulated to determine bounds on specific design parameters. This procedure is called *probing*. Results from probing and profiling are used to determine the design parameters which influence the solution most. Only those parameters are explored exhaustively, whereas the remaining parameters are considered with a sensitivity analysis which will be introduced later.

Mohanty et al. [83] use an analytical step first to prune the design space by symbolic constraint satisfaction. This information is used to limit the design space for trace-driven system-level simulations. Cycle and power accurate simulators may be used on the lowest level of abstraction. Results from accurate single component simulations can also be back-annotated to elements of the system simulation to improve results on a higher layer of abstraction.

In [98], different solutions of logic synthesis are explored. The problem description, e.g. a flow graph, is subdivided into templates of apparent regular structures, i.e. clusters of operations which can be found again and again in the graph. Results from exploring those templates can then be applied to all instances of the corresponding template. A further step searches the design space at the granularity of the supergraph consisting only of templates.

Baghdadi et al. [6] use a few individual building blocks which are synthesized to RT level in order to extract timing information for possible mappings on a higher level of abstraction, i.e., this information is back-annotated to a higher level of abstraction.

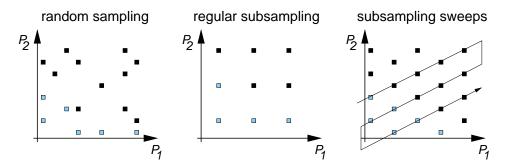

Subsampling of the design space. Subsampling the design space is a reasonable choice if the designer is interested in an unbiased exploration where an exhaustive search would be prohibitive. The subsampling pattern could be completely random, based on some regular grid, or biased by some expected shape of the design space and/or objective function(s). Monte-Carlo based searches, simulated annealing, and evolutionary optimizers (implementing mutation) use random subsampling patterns. All approaches which quantize design parameters to reduce the design space, e.g. by allowing only a set of fixed bit widths for architecture building blocks, apply a regular sampling pattern. This property translates, for instance, to the length of one step using hill climbing. In [109], defined sweeps across the design space of VLIW architectures are used to explore the design space. Fig. 6 shows some common sampling patterns.

Figure 6: Common approaches for subsampling the design space.

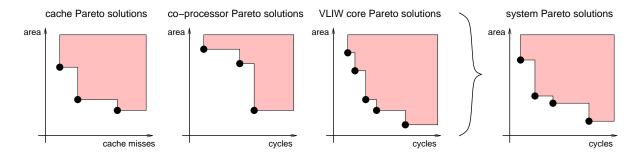

Subdividing the design space into independent parts for optimization. The goal of this approach is to reduce the number of possible designs by dividing the optimization problem into independent subproblems. In this way, we do not need to consider all possible combinations of design parameters but rather all combinations of Pareto solutions found for the subsystems (Fig. 7). Although the dimensions of the solution spaces for the different subsystems could be similar, e.g. cost and speed, the problem space of each of the subsystems usually comprises quite different, domain-specific parameters. A cache could be described by its size and organization, a VLIW core by its issue width and operator bit width, etc.

Kathail et al. [55] divide the optimization of an embedded computing system into separate optimizations of the cache memory hierarchy, a customized systolic array used as a co-processor, and a VLIW processor. The exploration of memory subsystems described in [79, 61] separates optimizations concerning power consumption (by determining the cache size), main memory size (by varying the data layout), and speed (by optimizing address calculations). Givargis et al. [37] describe a method where the designer initially defines clusters of design parameters which affect and depend on each other. Separate clusters can be explored independently. Then, Pareto-optimal configurations from clusters are merged.

Figure 7: Subdividing the design space into independent parts for optimization.

Sensitivity analysis of design parameters. The underlying assumption of this approach is the independence of design parameters. A sensitivity analysis of the design space is done using a set of reference benchmarks. In separate calibration runs only a single parameter is varied at a time, whereas all the other parameters are set to (fixed) arbitrary values. With each calibration step, the dynamic range of solution properties, such as power consumption and speed, is recorded.

Formally, given n design parameters  $P_i$ ,  $0 \le i < n$  with  $C_i$  possible configurations each, the number of possible configurations C for the overall system is the product of all parameter configurations

$$C = \prod_{i=0}^{n-1} C_i.$$

In order to reduce the number of configurations for evaluation, we perform the following experiments for each parameter  $P_i$  for all r reference benchmarks  $b_i$ ,  $0 \le j < r$ :

- Set all other parameters  $P_k$ ,  $0 \le k < n$ ,  $k \ne i$  to arbitrary (fixed) values  $P_k := P_{k_0}$ .

- Evaluate the system for all possible configurations  $C_i$  of parameter  $P_i$  and note the results of interest, for instance, in terms of speed.

- The system's sensitivity  $S_i$  to parameter  $P_i$  is then defined as the difference between the maximum and the minimum result in the series of results for all configurations of parameter  $P_i$ , i.e. in this example the difference between the maximum and the minimum achievable speed by varying  $P_i$ .

Given these results for the set of reference benchmarks, the sensitivities could be averaged among all benchmarks for each parameter. The design parameters  $P_i$  can then be sorted in decreasing order of sensitivity  $\{P_{S_{n-1}}, P_{S_{n-2}}, \dots, P_{S_0}\}$ , where  $P_{S_{n-1}}$  denotes the parameter with highest sensitivity and  $P_{S_0}$  the parameter with lowest sensitivity, respectively. The complexity of the design space exploration using these parameters can now be reduced by evaluating only designs defined by the sum of all parameter variations (versus multiplying all parameter variations in the exhaustive case) and by dropping parameters with small influence on the solution space from the exploration. For example, assuming that we stop evaluating the design space at parameter  $P_{S_q}$ , the resulting number of evaluations C' to perform for an unknown setup is given by

$$C' = \sum_{i'=S_q}^{S_{n-1}} C_{i'}.$$

Work described in [2, 3, 31, 48] uses sensitivity analysis to prune the design space. Ascia et al. [2] show one approach to extend sensitivity analysis to multiple objectives.

Constraining the design space. This straightforward task is listed as a separate point since the identification of design space constraints can form a significant initial step of a DSE run. The identification of corner cases of the design space could be done, for instance, by probing the design space or by worst-case analytical methods, such as the network calculus [66, 113] for the network processing domain and event-stream based methods for the real-time embedded domain [99].

## 4.5 Supporting functionality for automated DSE

The following approaches address practical issues that arise when dealing with implementing automated DSE, i.e. integrating legacy tools, working on several layers of abstraction, and reducing the resource requirements of the evaluation host computer.

Hierarchical simulator integration. The evaluation of IP-core based designs may require the integration of simulation frameworks from different manufacturers which may work on different levels of abstraction, e.g. functional versus cycle-accurate levels. In [76], a framework is presented that integrates different simulators. Problems that are specific to this integration are addressed, such as a description of how stimuli at low abstraction levels could be generated from high-level stimuli and how the state of low-level simulators can be maintained between simulation runs that are triggered by higher level simulators.

Validation: Equivalence check. A DSE run aimed to explore implementations for a tightly defined specification requires automated validations whether an implementation still meets the requirements of the specification. In the general case, formal verification tools address this problem. There also exist less complex approaches for well defined subproblems. For instance, in [51] a procedure is described to check two designs for equivalence of output traces. Searching the state space of both designs is avoided. Another partial verification technique is symbolic simulation (see [122] and the references therein) where the state space is subsampled by verifying system properties for defined symbolic inputs only. The effort spent for validation and verification can be reduced by employing correct-by-construction techniques. Architecture description languages, for instance, keep a central description of the micro-architecture of a processor to automatically derive correct compilers, simulators, and hardware descriptions from it.

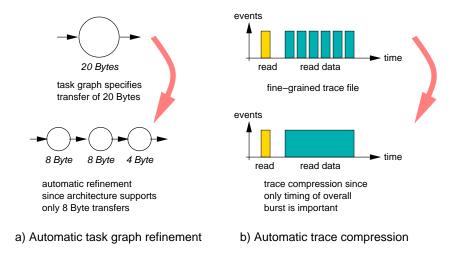

Automatic refinement of the task graph. Given a DSE problem which should be solved using the Y-chart [56] approach, specifications for applications may not necessarily match the features exported by the architecture description. Thus, in order to perform the mapping step, automatic adaptations of the specifications are required. In [94], automatic task graph refinements to cope, e.g., with synchronization and serialization of accesses are described. The same kind of problem is addressed in the work by Lieverse et al. [73] for trace-based simulation. In [64, 63], automatic refinements of communication traces are described to consider DMA block lengths and bus protocols. This principle is sketched in Fig. 8a.

**Trace compression.** Trace-driven simulations may require a large number of long traces. This is why research efforts also focus on compression and abstraction techniques for traces. Lahiri et al. [64, 63] show how communication traces could be abstracted from, e.g., burst transfers to only reveal abstract communication events as sketched in Fig. 8b.

**Synthetic trace generation.** In order to relief the designer from managing and recording traces for trace-based simulation, the synthetic generation of traces according to profiling information is described in [27] in order to use (legacy) trace-based tools.

Figure 8: Supporting functionality for automated DSE.

Coupling of incompatible building blocks. While designing a heterogeneous multi-processor system the designer faces the problem that he/she has to use architecture building blocks from different manufacturers and sources. As a consequence, the blocks might have been modeled at different levels of abstraction and provide different communication interfaces. So-called wrappers/ adapters [126, 106] are needed for simulation and synthesis to fit components together, which can affect hardware and software parts of the system. Knowledge from interface synthesis [75, 108, 89, 86] can be reused for the hardware part of a wrapper, whereas following the approach of Networks-on-Chip [106] based on standard network interfaces affects protocol stacks on programmable cores. A theory of adapters for event-stream models can also be used for analysing heterogeneous systems [100].